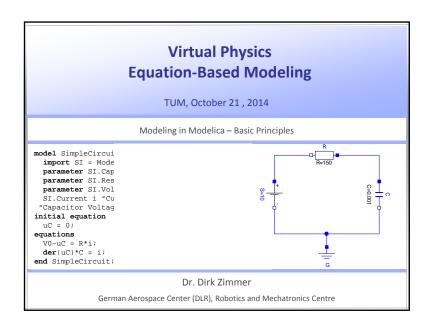

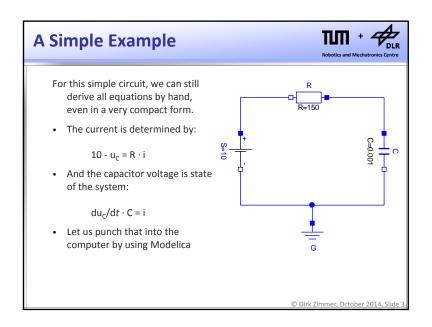

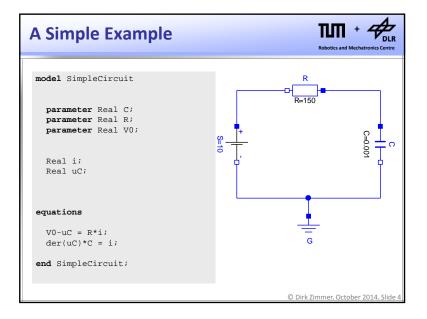

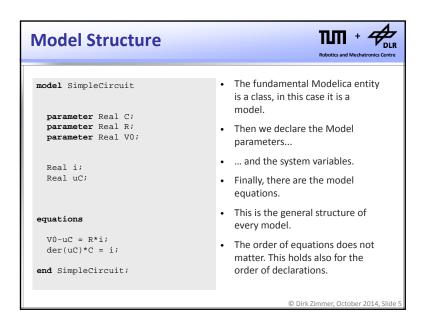

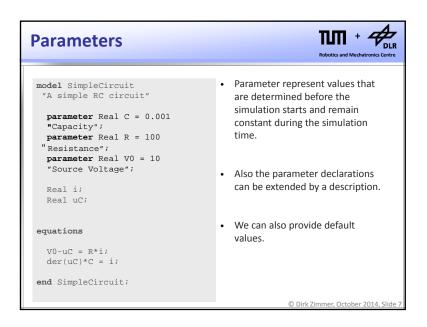

### **Model Structure** • Each model starts with the model SimpleCircuit "A simple RC circuit" header... parameter Real C; • ...and ends with a repetition of its parameter Real R; parameter Real V0; name. Real i; • We can add a model description Real uC; and indeed we should do so. equations V0-uC = R\*i;der(uC)\*C = i;end SimpleCircuit; © Dirk Zimmer, October 2014, Slide

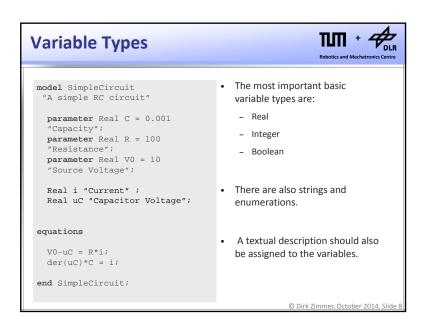

### **Equation Block** model SimpleCircuit Equations can be stated in any "A simple RC circuit" order. parameter Real C = 0.001 • The operator der(...) is a built-in "Capacity"; operator and represents the parameter Real R = 100 time-derivative "Resistance"; parameter Real V0 = 10 • IMPORTANT! The equation is not "Source Voltage"; causal: it is a non-causal relation between variables. It is not an Real i "Current" ; Real uC "Capacitor Voltage"; assignment! If we want to state a causal equations assignment we can use V0-uC = R\*i;instead of der(uC)\*C = i; end SimpleCircuit; © Dirk Zimmer, October 2014, Slide

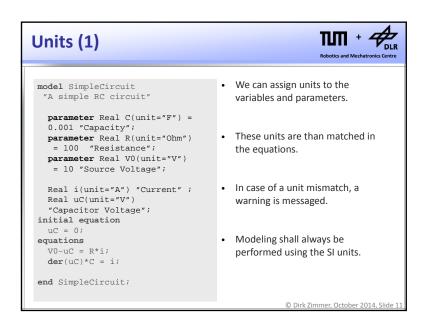

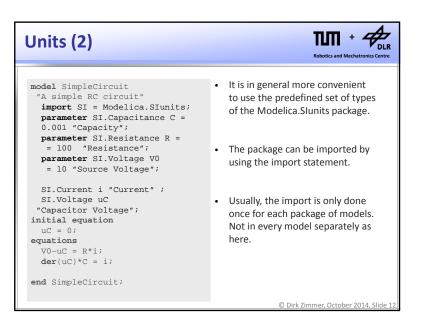

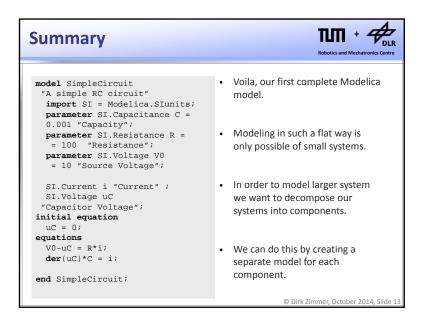

### **Initial equations** model SimpleCircuit We are still missing the initial "A simple RC circuit" equations. parameter Real C = 0.001 "Capacity"; • They can be stated in a separate parameter Real R = 100 "Resistance"; block. parameter Real V0 = 10 "Source Voltage"; · If there is a insufficient number of Real i "Current" ; Real uC "Capacitor Voltage"; initial equations, Dymola will assume zero (or a nominal value) initial equation for the remaining undetermined uC = 0;variables. equations V0-uC = R\*i;der(uC)\*C = i; Also a warning is displayed. end SimpleCircuit; © Dirk Zimmer, October 2014, Slide 1

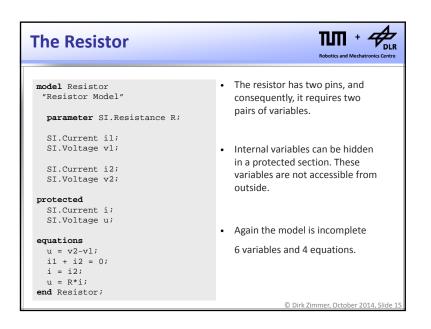

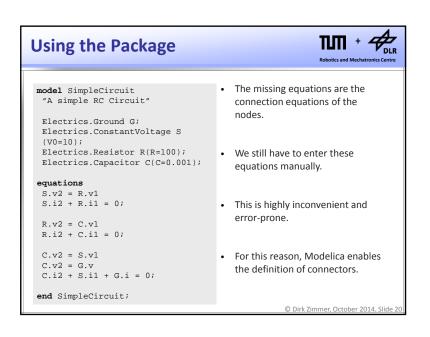

### **The Ground Model** As we have learned last lecture. model Ground "Ground Element" the ground is represented by a pair of variables SI.Current i; SI.Voltage v; The voltage potential v equations - The current i v=0;end Ground; • Please note that the model is incomplete. Two variables but just one equation. • The missing equations will be added when we connect the component within the circuit. © Dirk Zimmer, October 2014, Slide 1-

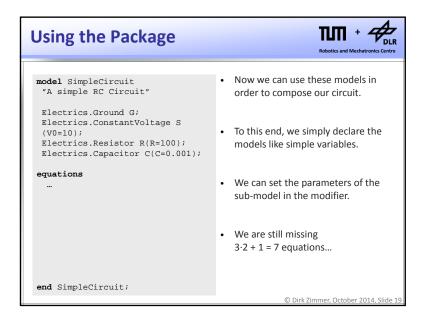

### **Creating a Package** · All these models can be collected package Electrics "Basic Electric Elements" in a Modelica package import SI = Modelica.Slunits; · A package can contain arbitrary classes, also sub-packages. model Ground • The look-up of class-names end Ground; within a package is first done locally within a class and then model Resistor further up the hierarchy. end Resistor; • Hence, the import statement is model Capacitor valid for all models in the package. end Capacitor; • Identifiers of instances (variables or components) are only looked up locally. end Electrics; © Dirk Zimmer, October 2014, Slide 1

# Connectors connector Pin SI.Voltage v "Potential at the pin"; flow SI.Current i "Current flowing into the pin"; end Pin; This is the definiton of the corresponding connector. It consists in a set of variables. These variables can be declared to be... potential variables: SI.Voltage v flow SI.Current i

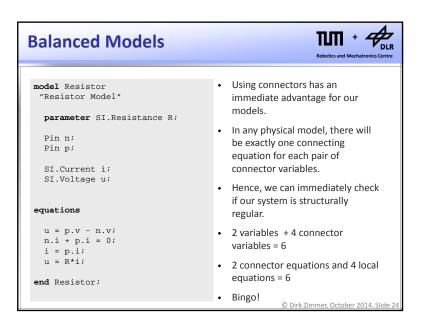

### **Modeling with Connectors** • Let us integrate the pin connector model Resistor "Resistor Model" in our Resistor model. parameter SI.Resistance R; • To this end, we declare two pins Pin n; Pin p; SI.Current i; · We can access the connector SI.Voltage u; variables like any other variables. equations • Likewise, the procedure is done u = p.v - n.v;for all other components n.i + p.i = 0;i = p.i;u = R\*i;end Resistor; © Dirk Zimmer, October 2014, Slide 2

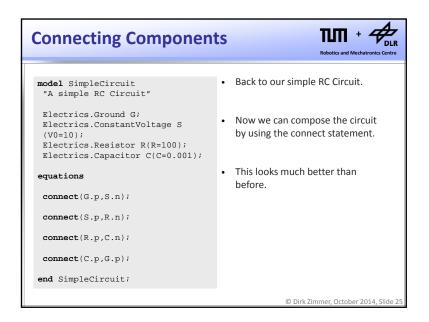

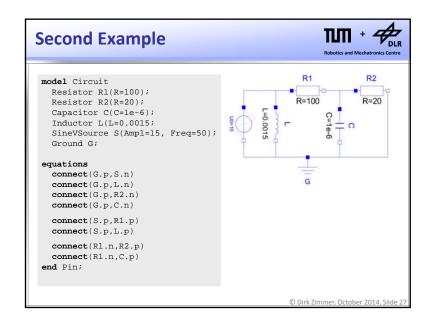

## connector equations connector Pin SI.Voltage v "Potential at the pin"; flow SI.Current i "Current flowing into the pin"; end Pin; • We can link two ore more pins by using the connect statement. connect(pin1, pin2) connect(pin1, pin3) pin1.v = pin2.v pin1.v = pin3.v pin1.i + pin2.i +pin3.i = 0 • The equations are generated in dependence on the declaration • Connections form a graph that represents a wood and that is component relevant and structure irrelevant.

© Dirk Zimmer, October 2014, Slide 2

### **Inheritance**

## partial model OnePort SI.Voltage u;

SI.Current i;

Pin p; Pin n;

### equation

u = p.v - n.v; 0 = p.i + n.i; i = p.i; end OnePort;

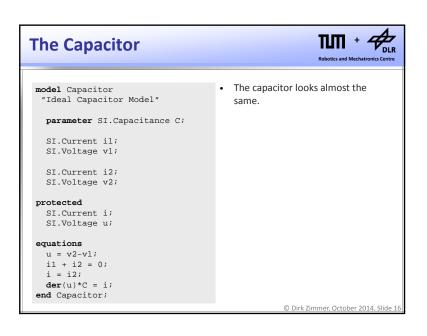

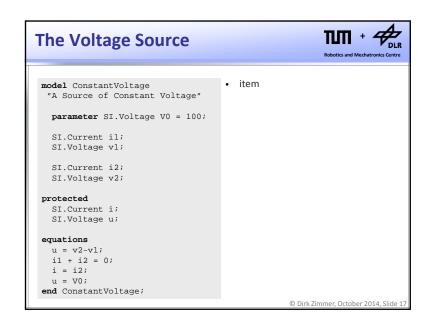

- We already noticed that the resistor, capacitor, and voltage source share most of their equations.

- We can share this common part by declaring an abstract base model.

- The base model can serve as template for many concrete models.

- It is denoted as partial, since there are equations missing and the abstract base model should not be instantiated.

© Dirk Zimmer, October 2014, Slide 2

### **Inheritance**

- New models can be generated out of the partial base model by the keyword extends.

- Then the missing parameters and equations are added.

- The keyword extends can be applied in a very generic way.

- Multiple inheritance is possible as well.

model Capacitor

extends OnePort;

parameter

SI.Capacitance C=1;

equation

der(u)\*C = i;

end Capacitor;

model Resistor

extends OnePort;

parameter

SI.Resistance R=1;

equation

u = R\*i;

end Capacitor;

© Dirk Zimmer, October 2014, Slide 3:

### **Inheritance**

partial model OnePort

SI.Voltage u; SI.Current i;

Pin p; Pin n;

### equation

u = p.v - n.v; 0 = p.i + n.i; i = p.i;

end OnePort;

${f model}$  Capacitor

extends OnePort;

parameter

SI.Capacitance C=1;

equation

der(u)\*C = i;

end Capacitor;

model Resistor

extends OnePort;

parameter

SI.Resistance R=1;

equation

u = R\*i;

end Capacitor;

© Dirk Zimmer, October 2014, Slide 30

### **Conclusions**

Let us conclude by a few general remarks

- Modelica provides means to express differential-algebraic equation systems in a convenient way.

- Modelica enables to organize the knowledge in a hierarchical form.

- Modelica is a declarative modeling language. It is not a programming language.

- The declarative style enables the modeler to focus on what he wants to model rather than to think about how to achieve a computational realization.

- In this way, the models become also more self-contained. They represent meaningful semantic entities by themselves even without being simulated.

© Dirk Zimmer, October 2014, Slide 32